#### Even worse

#### The way to do it

#### Metastability resolution time

#### Flip-flop metastable behavior

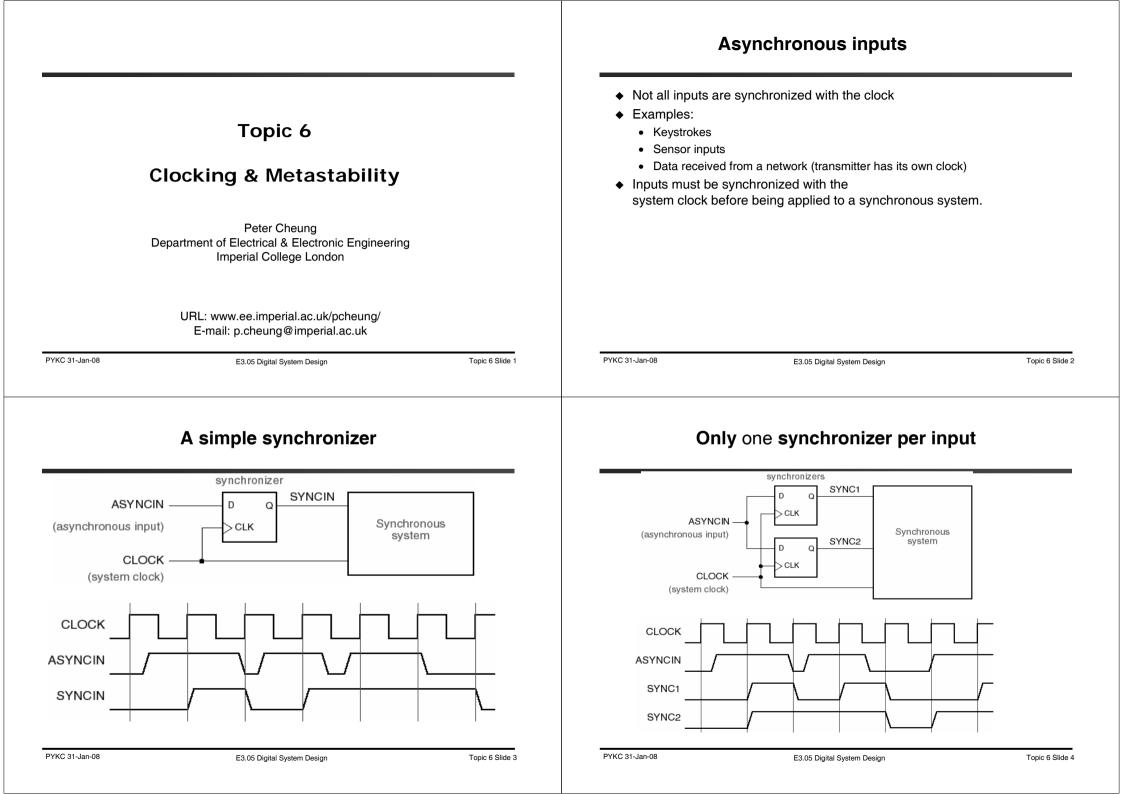

- Probability of flip-flop output being in the metastable state is an exponentially decreasing function of t<sub>r</sub> (time since clock edge, i.e. "resolution time").

- Stated another way,

$$MTBF(t_r) = \frac{\exp(t_r / \tau)}{T_o f a}$$

where

$\tau$  and  $T_0$  are parameters for a particular flip-flop, *f* is the clock frequency, and *a* is the number of asynchronous transitions / sec

E3.05 Digital System Design

Topic 6 Slide 10

# Typical flip-flop metastability parameters

|                                                                     | Device           | τ <b>(ns)</b> | T <sub>o</sub> (s)   | t <sub>r</sub> (ns) |

|---------------------------------------------------------------------|------------------|---------------|----------------------|---------------------|

| $MTBF(t_r) =$                                                       | 74LS74           | 1.50          | $4.0\cdot 10^{-1}$   | 77.71               |

| $\frac{\exp\left(t_r / \tau\right)}{T_o f a}$                       | 74S74            | 1.70          | $1.0 \cdot 10^{-6}$  | 66.14               |

|                                                                     | 74S174           | 1.20          | $5.0\cdot10^{-6}$    | 48.62               |

|                                                                     | 74S374           | 0.91          | $4.0\cdot 10^{-4}$   | 40.86               |

| MTBF = 1000 yrs.<br>F = 25 MHz<br>a = 100 KHz<br>t <sub>r</sub> = ? | 74F74            | 0.40          | $2.0\cdot 10^{-4}$   | 17.68               |

|                                                                     | PALC16R8-25      | 0.52          | $9.5\cdot 10^{-12}$  | 14.22*              |

|                                                                     | PALC22V10B-20    | 0.26          | $5.6 \cdot 10^{-11}$ | 7.57*               |

|                                                                     | PALCE22V10-7     | 0.19          | $1.3 \cdot 10^{-13}$ | 4.38*               |

|                                                                     | 7300-series CPLD | 0.29          | $1.0\cdot 10^{-15}$  | 5.27*               |

|                                                                     | 9500-series CPLD | 0.17          | $9.6\cdot 10^{-18}$  | 2.30*               |

|                                                                     |                  |               |                      |                     |

PYKC 31-Jan-08

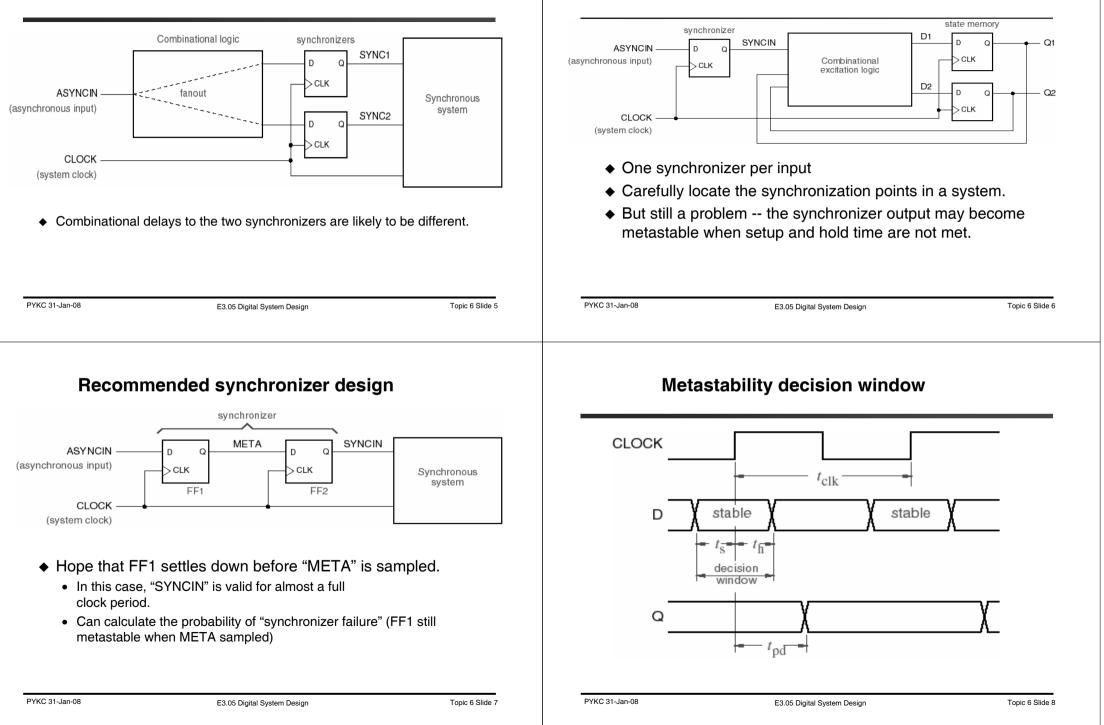

## Is 1000 years enough?

#### Multiple-cycle synchronizer

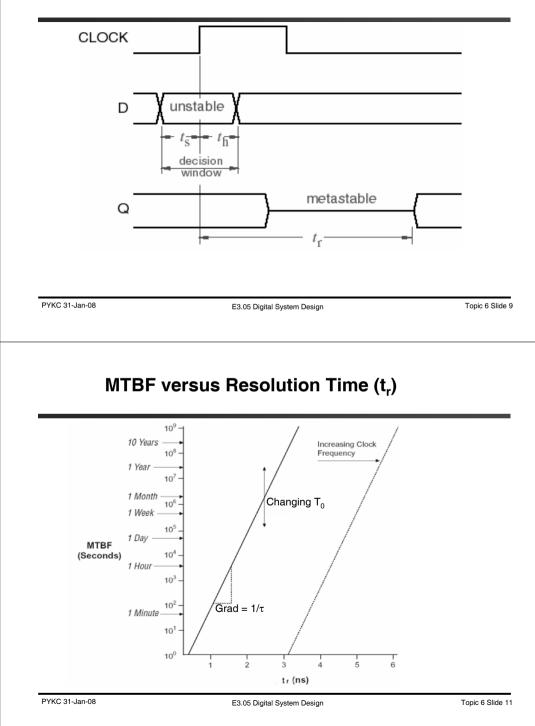

#### **Clock-skew calculation**

#### Example of bad clock distribution

CLOCK

CLOCK1

CLOCK2

CLOCK L

$t_{\rm ffpd(min)} + t_{\rm comb(min)} - t_{\rm hold} - t_{\rm skew(max)} > 0$

- First two terms are minimum time after clock edge that a D input changes

- Hold time is earliest time that the input may change

- Clock skew subtracts from the available hold-time margin

- Compensating for clock skew:

- Longer flip-flop propagation delay

- Explicit combinational delays

- Shorter (even negative) flip-flop hold times

| PYKC 31-Jan-08 | E3.05 Digital System Design | Topic 6 Slide 17 | PYKC 31-Jan-08 | E3.05 Digital System Design | Topic 6 Slide 18 |

|----------------|-----------------------------|------------------|----------------|-----------------------------|------------------|

|                |                             |                  |                |                             |                  |

|                |                             |                  |                |                             |                  |

CLOCK

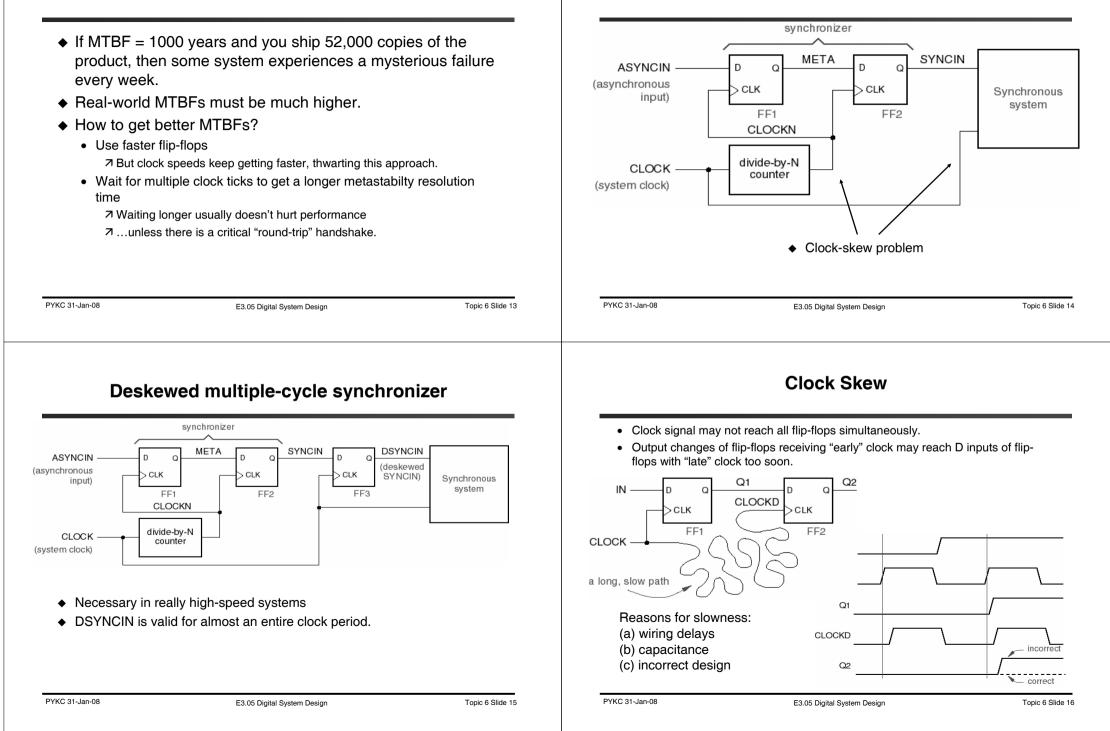

## **Multiple Clock Domains**

Many digital systems have more than one clock domains:-

- Needs to synchronise the two clock domains using two basic building blocks:

- Phase-locked loop (PLL)

- Delay-locked loop (DLL)

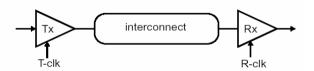

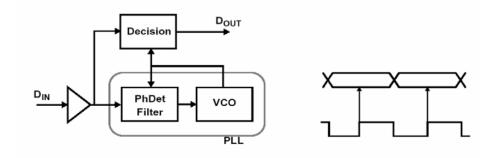

#### **Example: Classical clock recovery**

- Clocking information embedded in data stream

- Use PLL to recover the clock

- State of system is stored in analog loop filter

PYKC 31-Jan-08

all in same IC package

CLOCK1

CLOCK2

**CLOCK3**

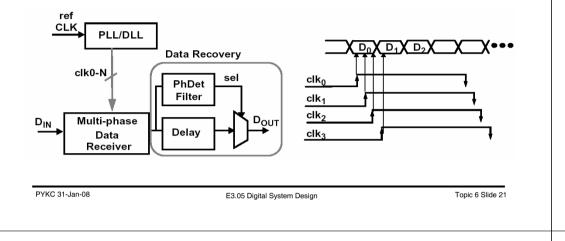

#### **Oversampled Clock/Data Recovery**

- Oversample the data and perform phase alignment digitally

- De-couples clock generation from tracking of data •

- Data must guarantee transitions to ensure tracking

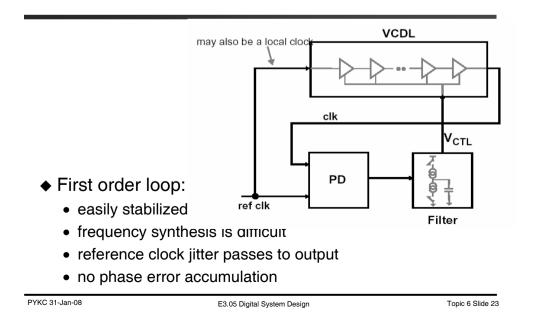

# What is a Delay locked loop?

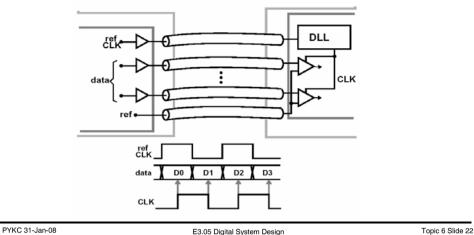

#### Phase Alignment in Source Synchronous Systems

- Timing information carried by reference clock

- ◆ Use DLL to ensure proper clock phase for sampling

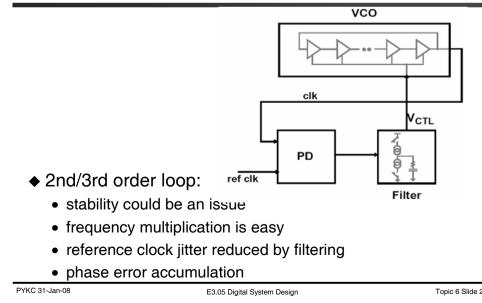

### What is Phase locked loop?

#### **Timing Loop Performance Parameters**

# <section-header> Phase Jitter Clock w/o jitter Clock w/o jitter Clock w/o jitter Clock w/o jitter Time Domain Frequency Domain Frequency Domain Frequency Domain Standwidth Inste at which output phase and reference phase Acquisition time (to lock) Frequency range (lock range)

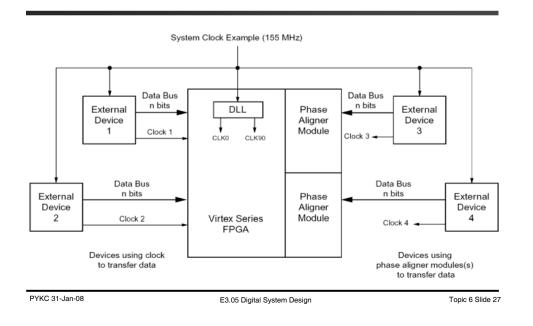

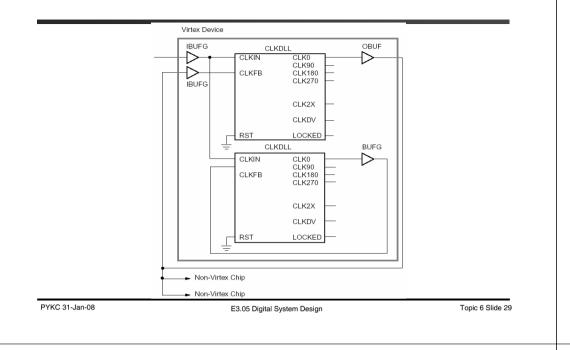

### **Clock Management with DLL**

- Can eliminate on-chip clock delay

- can also eliminate on-board clock delay

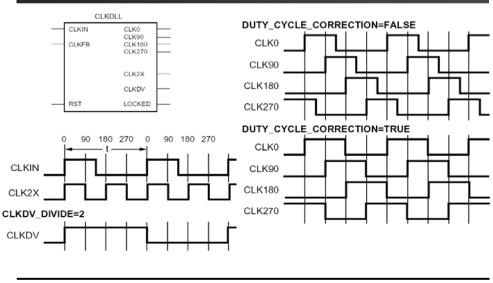

- ◆ 4 fixed-phase outputs (0°, 90 °, 180 °, 270 °)

- Selectable phase shift (n / 256 of the period)

- through configuration

- or through increment/decrement

- 1/256 of clock period or 50 picosecond granularity

- Frequency synthesis (division and multiplication)

- ◆ Outputs are always phase-coherent

# Solves the speed problem of large chips

| PYKC 31-Jan-08 | E3.05 Digital System Design | Topic 6 Slide 25 | PYKC 31-Jan-08 | E3.05 Digital System Design | Topic 6 Slide 26 |

|----------------|-----------------------------|------------------|----------------|-----------------------------|------------------|

|                |                             |                  |                |                             |                  |

|                |                             |                  |                |                             |                  |

#### DLL in Xilinx Virtex data/clock alignment

# Xilinx DLL with various phase outputs

PYKC 31-Jan-08

#### Using DLL to de-skew onboard clock signals

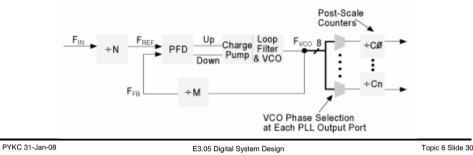

#### Altera Cyclone II PLL (1)

- Phase-locked loop (PLL) is a closed-loop frequency-control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator.

- Main components:

- Phase frequency detector (PFD)

- Charge pump & loop filter

- Voltage controlled oscillator (VCO)

- Counters (N pre-scale, M feedback, C post-scale)

# Altera Cyclone II PLL (2)

- PLL aligns the rising edge of reference input clock to feedback clock using the PFD.

- PFD detects difference in phase and frequency between reference clock and feedback clock and generates an "up" or "down" control signal based on whether the feedback frequency is lagging or leading the reference frequency.

- If the charge pump receives an up signal, current is driven into the loop filter, otherwise, current is drawn from the loop filter.

- Loop filter converts these "up" "down" signals to a control voltage to control the oscillation frequency of the voltage controlled oscillator (VCO).

- Feedback loop counter (M) is used to increase VCO frequency above input reference frequency.

- Pre-scale counter (N) is used to produce the reference frequency from F<sub>IN</sub>.

- The post-scale counters (C) allows a number of harmonically related frequencies be generated from one common clock.

# Altera Cyclone II PLL (3)

- The output frequency is given by:

- $F_{REF} = F_{IN} / N$

- $F_{VCO} = F_{REF} \times M = F_{IN} \times M/N$

- $F_{OUT} = F_{VCO} / C = (F_{REF} \times M) / C = (F_{IN} \times M) / (N \times C)$

#### where:

- F<sub>VCO</sub> = VCO frequency

- F<sub>IN</sub> = input frequency

- F<sub>REF</sub> = reference frequency

- F<sub>OUT</sub> = output frequency

- M = counter (multiplier), part of the clock feedback path

- N = counter (divider), part of the input clock reference path

- C = post-scale counter (divider)

E3.05 Digital System Design

Topic 6 Slide 31

#### **References for this topic**

- Chapter 8, pp757-773, Digital Design Principles & Practices, John Wakerly.

- "Metastability in Altera Devices", Altera App Note 42.

- "Using the ClockLock & ClockBoost PLL Features in APEX Devices", Altera App Note 115.

- "Using the Virtex Delay-Locked Loop", XAPP-132.

- "Advantages of APEX PLLs Over Virtex DLLs", Altera TB60.

PYKC 31-Jan-08

E3.05 Digital System Design

Topic 6 Slide 33